Merge pull request #3661 from whik/whik_sf2

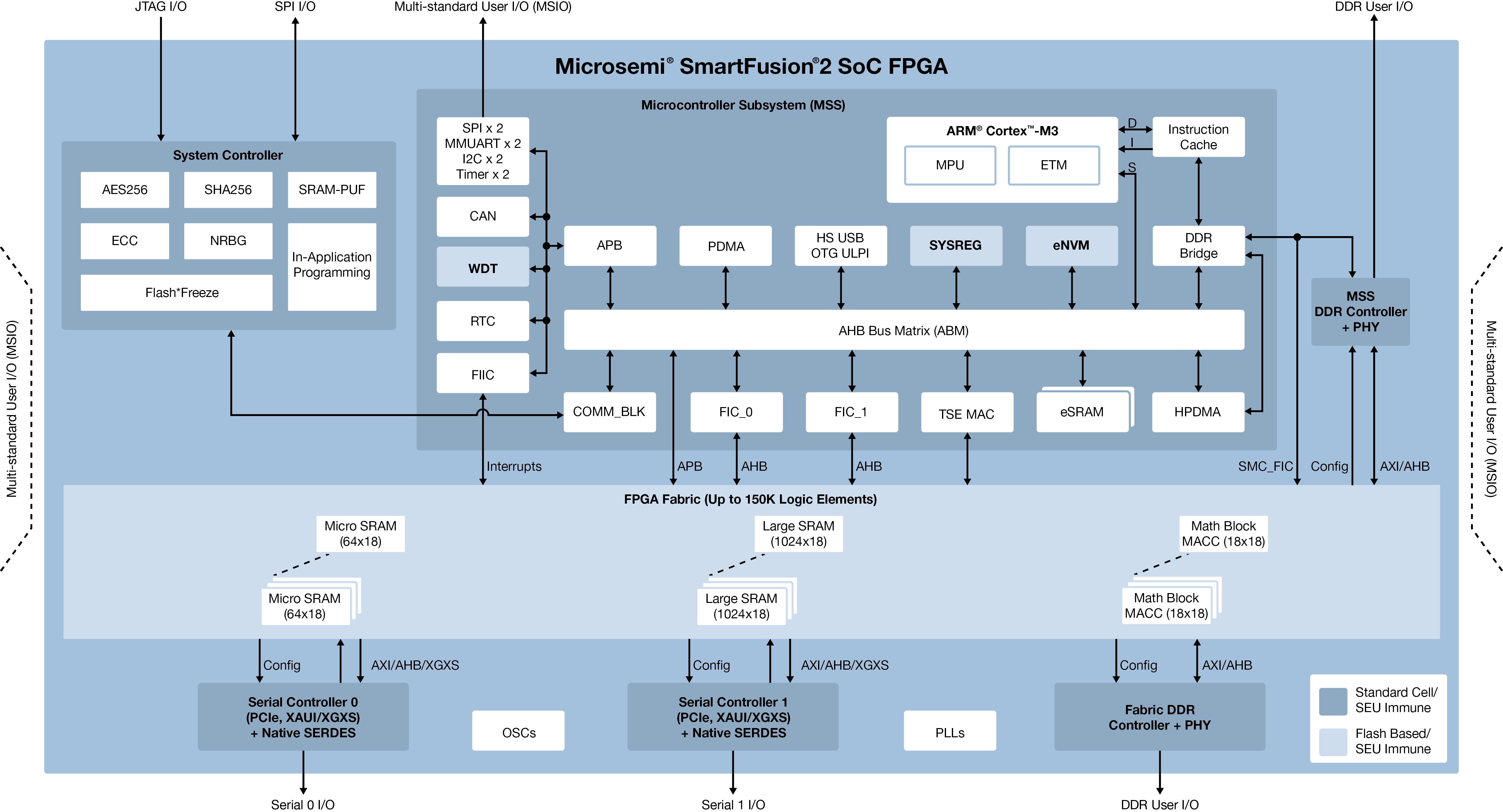

add support for Microsemi SmartFusion2 family FPGA

Showing

bsp/smartfusion2/CMSIS/SConscript

0 → 100644

bsp/smartfusion2/CMSIS/core_cm3.c

0 → 100644

bsp/smartfusion2/CMSIS/core_cm3.h

0 → 100644

此差异已折叠。

bsp/smartfusion2/CMSIS/m2sxxx.h

0 → 100644

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

bsp/smartfusion2/Kconfig

0 → 100644

bsp/smartfusion2/README.md

0 → 100644

此差异已折叠。

bsp/smartfusion2/SConscript

0 → 100644

bsp/smartfusion2/SConstruct

0 → 100644

此差异已折叠。

bsp/smartfusion2/board/SConscript

0 → 100644

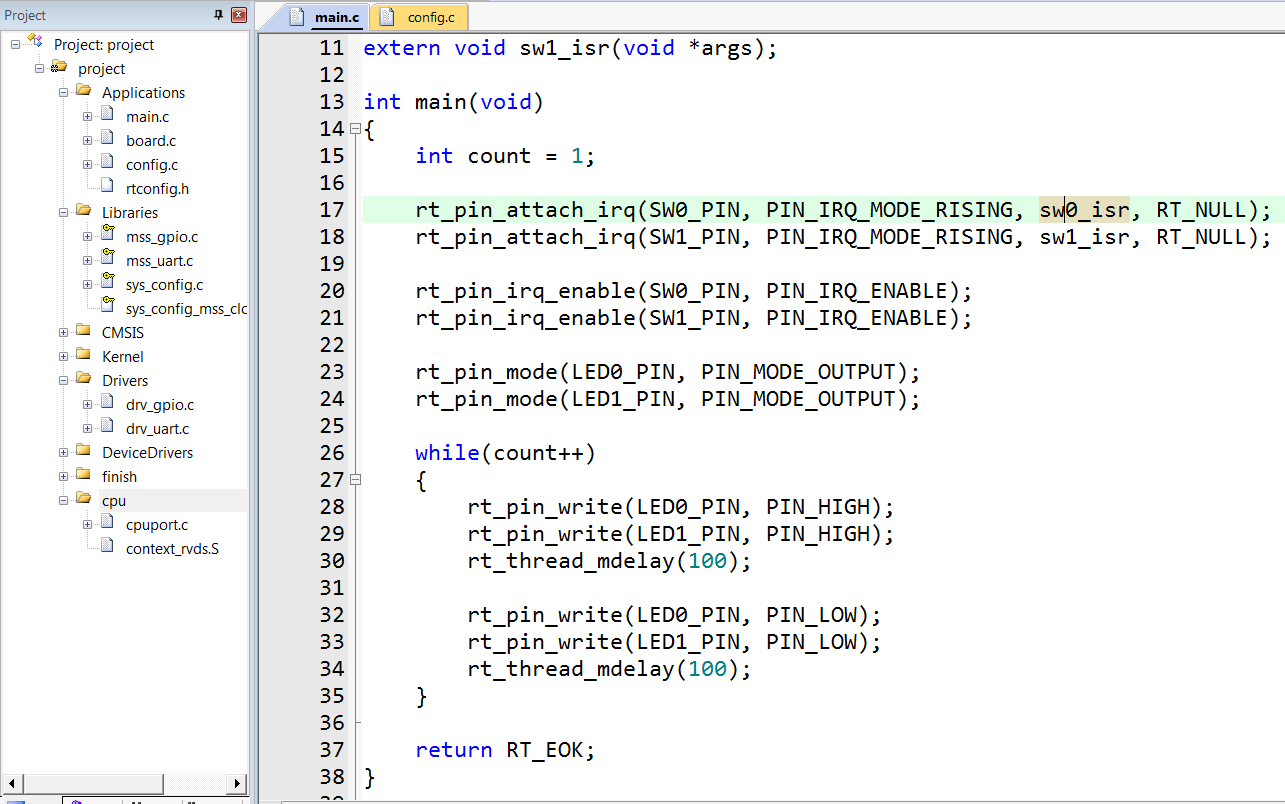

bsp/smartfusion2/board/board.c

0 → 100644

此差异已折叠。

bsp/smartfusion2/board/config.c

0 → 100644

此差异已折叠。

bsp/smartfusion2/board/config.h

0 → 100644

此差异已折叠。

bsp/smartfusion2/drivers/Kconfig

0 → 100644

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

1006.8 KB

581.0 KB

157.8 KB

154.4 KB

151.7 KB

bsp/smartfusion2/figures/log.jpg

0 → 100644

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

bsp/smartfusion2/project.uvopt

0 → 100644

此差异已折叠。

bsp/smartfusion2/project.uvoptx

0 → 100644

此差异已折叠。

bsp/smartfusion2/project.uvproj

0 → 100644

此差异已折叠。

bsp/smartfusion2/project.uvprojx

0 → 100644

此差异已折叠。

bsp/smartfusion2/rtconfig.h

0 → 100644

此差异已折叠。

bsp/smartfusion2/rtconfig.py

0 → 100644

此差异已折叠。

bsp/smartfusion2/template.uvopt

0 → 100644

此差异已折叠。

bsp/smartfusion2/template.uvoptx

0 → 100644

此差异已折叠。

bsp/smartfusion2/template.uvproj

0 → 100644

此差异已折叠。

bsp/smartfusion2/template.uvprojx

0 → 100644

此差异已折叠。