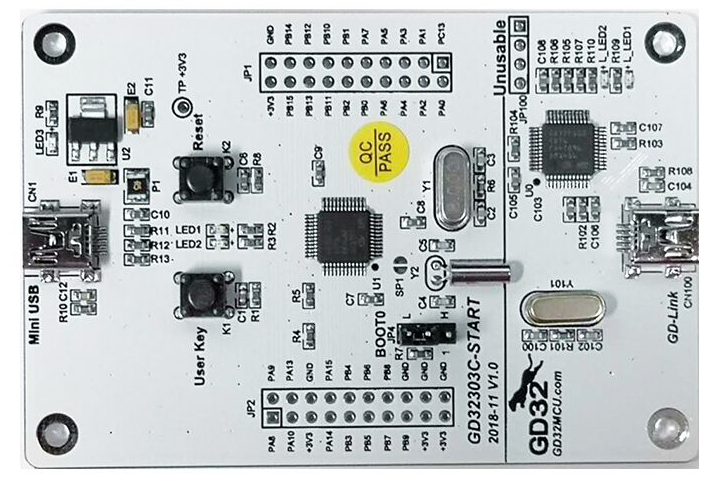

[GD32][BSP]添加GD32303C-START开发板 (#6465)

* first copy * [GD32][BSP]添加GD32303C-START开发板 * 更新yml文件 * 更新scons脚本

Showing

此差异已折叠。

437.8 KB

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。